In theory, physical synthesis tools have all the necessary information about the layout; in practice, they must also be very carefully associated with the actual layout data. The entire physical design process for a large design can take many days to complete. Therefore, if you can provide feedback to the design and architecture team as early as possible so that they can plan timing constraints and freely and quickly take advantage of layout options, they will be able to create valuable value. To achieve these goals, timing and area must be reliably estimated. The first attempt to solve this problem is to tighten the frequency. In other words, we try to synthesize at a higher frequency and then switch to a slightly lower frequency during the layout and routing phases. But this solution did not solve the problem. Another attempt is to reduce the timing of the nets and units. In fact, reducing the timing is to increase the coefficient that makes the unit process slower or faster. We tried a few numbers. Another direction we explore is to increase the relevance of extracting numbers. This is done by applying coefficients to the extracted net resistance and capacitance (RC) values. These values ​​directly affect the delay of the net by changing its RC value and affect the delay of the unit by changing its load capacitance. We have seen that in advanced processes, resistors have a huge impact on timing and area. Although in theory the physical synthesis tools have all the necessary information about the layout, in practice they must still be very carefully associated with the actual layout data. This process can be time consuming, but the benefits clearly outweigh the costs. At the end of the day, the best practice is to maintain a reliable correlation between the various steps in the design process, resulting in a fast, flexible design and a clear understanding of the ultimate goal from the start. Iphone Screen Protector,Tempered Glass,Privacy Tempered Glass,Hydrogel Screen Shenzhen TUOLI Electronic Technology Co., Ltd. , https://www.szhydrogelprotector.com

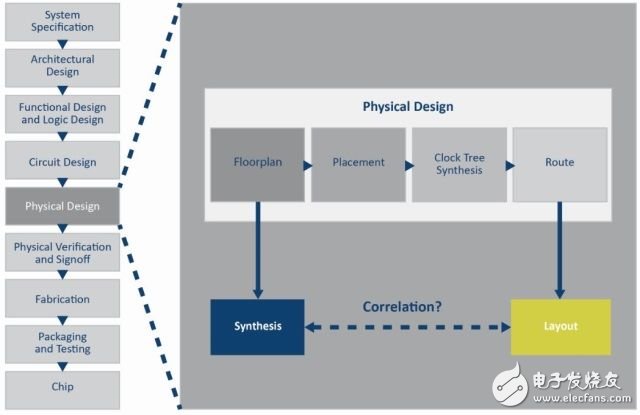

The design of a chip involves many stages, from system specification and architecture design, to various manufacturing methods and to the final packaging of the finished chip. Accurately estimating timing and area during this cycle will be critical as it will allow for accurate planning and product compliance. This article describes the physical design (or back-end design) portion of this process, specifically correlating timing and area in steps related to physical design.

Integrated circuit (IC) design flow and physical design steps (Figure 1)

In the past, we have mastered the correlation between integrated layout and routing. For timing, the accuracy is around 3% to 4%, and the area results are even better. But in the new advanced process, we have encountered more and more unexpected results since the 28-nm process node. Not only do we see a larger gap between the physical synthesis results and the actual timing of the layout and routing, but we also see that some of the timing paths become significantly faster, while other timing paths are much slower, which is quite confusing. When viewing the area, the results are even more worrying. From synthesis to layout, the correlation has become quite poor, as shown in the following figure:

Comparison of integrated cell density between layout planning stage (top) and layout phase (bottom) (Figure 2)

The picture above is the cell density map of the CEVA-XM4 core, comparing the cell density of the synthesis phase (top) and the layout phase (bottom). The orange portion of the layout stage image shows a significant increase in area. In this case, the overall increase in area is around 18%. This is very bad, but maybe it can be tolerated. But considering that most designs are fixed areas (memory and registers), from synthesis to layout will not change at all, it is clear that some parts do exceed the maximum limit. After separating the buffer unit area, we found that the combined area increased by 118%, which means that the number and area of ​​buffers more than doubled.

In areas where the ultimate cell density (marked in orange) is reached, the layout tool finds it difficult to determine the proper layout of the cell and iterate over multiple iterations, so it takes a lot of time to converge.

From the point of view of electrical engineering, we know that as the process technology shrinks, the role of the resistor will become more and more prominent. On the one hand, the capacitance of the wires remains approximately the same (or at least in the same order). On the other hand, the resistance will become higher and higher. In addition, at the advanced process nodes, the resistance of the top two metal layers is much lower than that of the other layers. And this also means that for layout tools, deciding which wires go to the higher layers and which wires remain at the lower layers becomes more and more problematic. The most affected, of course, is a buffered long-term network. This is why there is such a significant increase in buffer area, and the timing associated with long-term networks will deteriorate.

Comparison of the integrated cell density between the layout planning phase (top) and the post-application phase (bottom) (Figure 3)

We have found that more and more resistors provide better area correlation and timing correlation. The factors that are designed to achieve good correlation vary. As shown in the figure above, after applying the coefficients to the resistance, the correlation between the synthesis and the layout is significantly improved. We compare the combined area (top) with the layout area (bottom) again. As can be seen from the orange area of ​​the layout image, there is still a significant amount of high utilization load, but much less than before. In this example, the accuracy is around 5%, which is quite reasonable and will result in a good and efficient workflow.