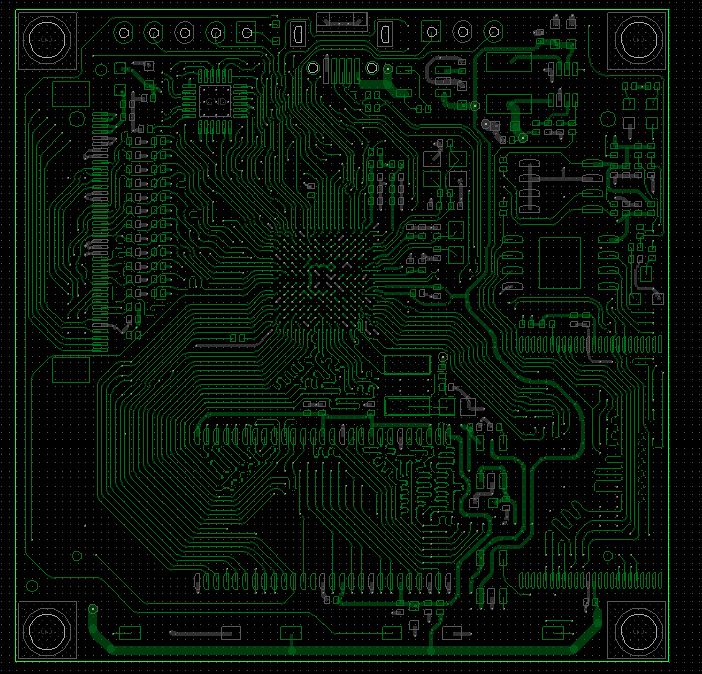

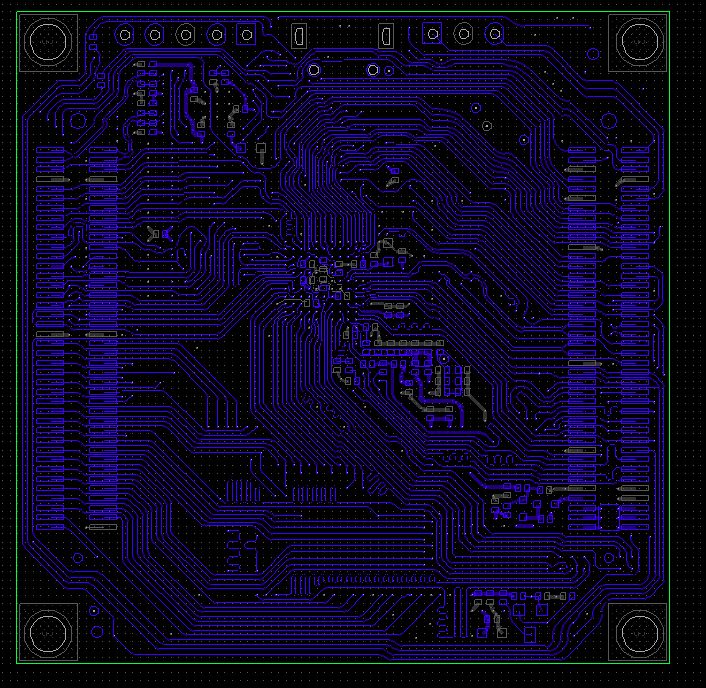

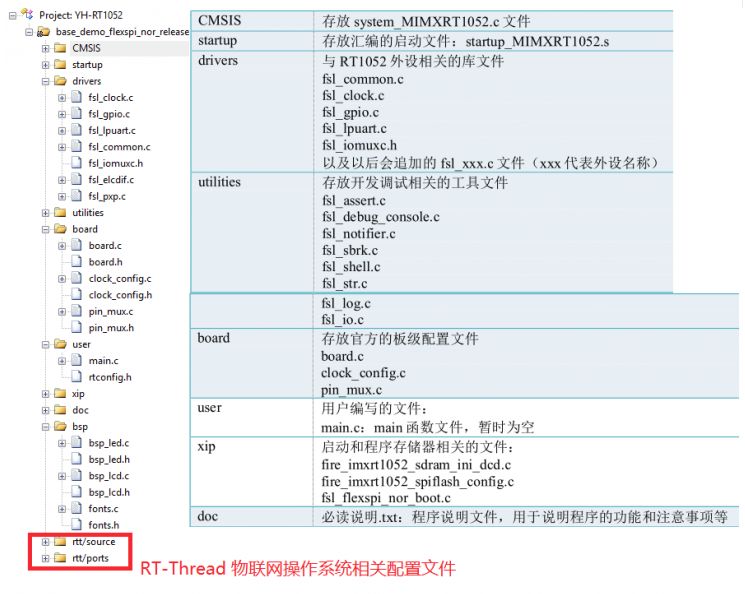

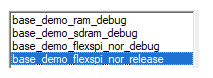

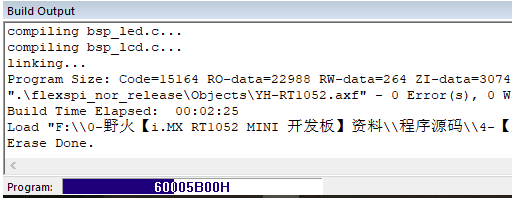

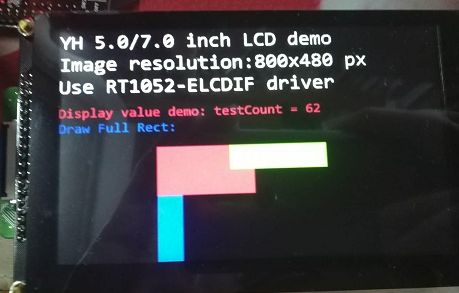

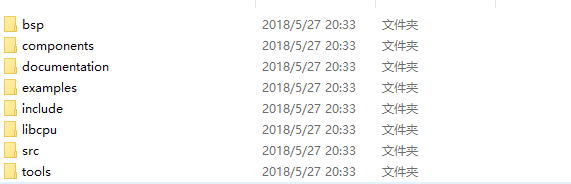

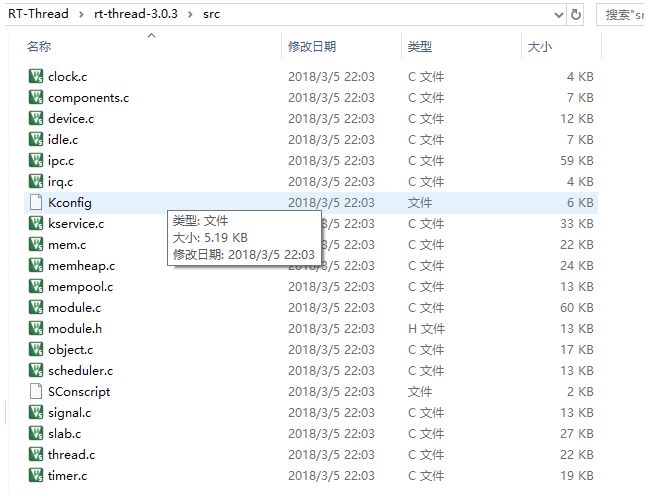

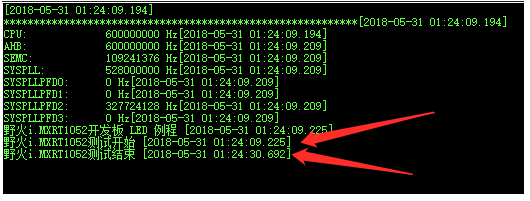

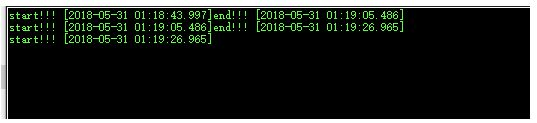

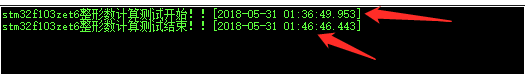

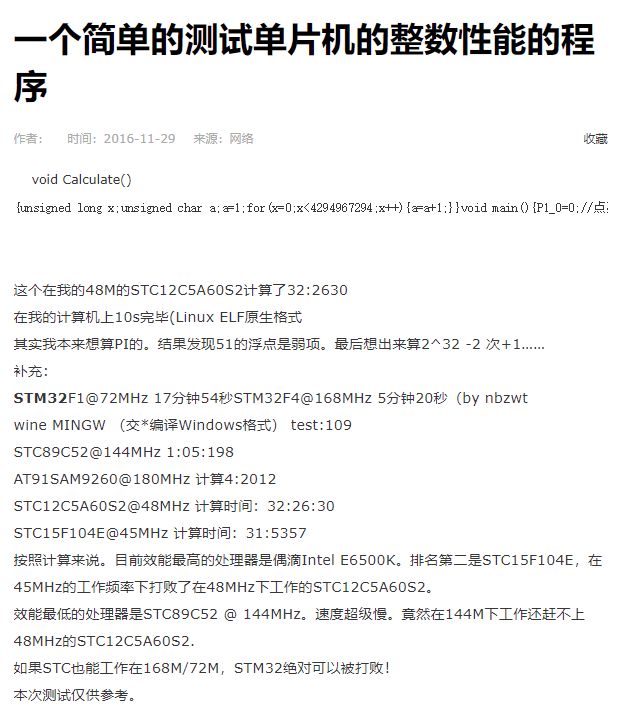

i.MX RT1052 is the i.MX RT series chip, which is a cross-border processor chip introduced by NXP Semiconductors. The series includes i.MX RT1020, i.MX RT1050 and i.MX RT1060 sub-series chips. The so-called "cross-border" means that its own positioning is neither a traditional application processor nor a traditional microcontroller. Traditional application processors such as mobile phone main control chip, they usually use ARM's Cortex-A series core, with its chip architecture allows the chip to achieve higher frequency operation. Traditional microcontrollers are also called MCUs. They usually use ARM's Cortex-M series cores. Relatively speaking, the cores have faster response to interrupts, so they have good real-time performance, but their chip architecture is especially integrated with an on-chip flash memory. The limitations of production technology and the cost burden limit their performance. The i.MX RT series chip integrates the advantages of both. It is based on the chip architecture of the application processor and uses the Cortex-M7 core of the microcontroller, which has the high performance and rich functions of the application processor, and also has the traditional Easy-to-use, real-time and low-power features of the microcontroller. Wildfire i.MX RT1052 core board equipped with i.MX RT1025DVL6A chip, Cortex-M7 core, clocked up to 600M. All 130 IOs are exported. Integrated 32MB SDRAM, 128MB NAND FLASH, 32MB QSPI FLASH, 2Kb EEPROM, LCD-RGB565 FPC interface, 1 SWD debug interface, 1 uart debug interface, 1 power LED, 1 user LED, 1 reset button, 1 MODE Buttons, 1 WAKEUP button, and 1 Microusb interface. A total of 130 chips, I0, are all pulled out through the 0.8mm BTB interface on the back, including the SEMC bus, which allows us to expand various modules. The bottom panel image is as follows: Installed in the mini floor effect chart, hey, JJ is still very envious of Pro floor, rich in resources. Even the LCD can be placed on the board, and my LCD can only get out through the cable. Look at the coquettish core of Firecore's core board: The top Bottom There was a lot of anger, but many signal lines use the same length to ensure the stability of the signal. This is worthy of praise!!! Introduce the performance advantages of i.MX RT1052 chip: 1. No need for on-chip flash memory Because the cross-border processor employs an application processor architecture with significantly smaller SRAM bit cells, in a cross-over design architecture, the SRAM can be configured as a TCM with “zero-wait†single-cycle access, significantly improving system performance. 2. High performance On-chip caches with high-density on-chip TCMs or caches can have cache miss rates as low as 1–2%, thus providing significantly better performance than MCUs. 3. Low interrupt latency Interruptions play an important role in embedded systems in coordinating timely responses to internal and external hardware events. The role they play in real-time systems that interact with users is particularly important because external events triggered by user input require the CPU to make reliable, low-latency, immediate responses. Cross-border processors are built using MCU cores, so even if they use an application processor architecture, they continue the important feature of low interrupt latency. The cross-border processor's interrupt latency can be as low as 10-20ns, while the application processor's latency is typically as long as 1ms. 4. High energy efficiency and safety. Now let's talk about the project written by the firmware library, according to the code style that Fire Brother has always been comfortable with. And the project contains different versions of the project Normally, we can't write code successfully. We need to debug for a long time to get the result. We can quickly load the program into the internal RAM of the RT1052 chip on our development board or the on-board SDRAM chip through ram_debug or sdram_debug version. Among them, to achieve rapid debugging code, but the RAM space is small, suitable for small program debugging, and onboard sdram has 32MB of space, suitable for debugging of large programs. However, when power is lost, these programs are lost and cannot be used on the product. Only debugging is required. The following two versions can be used as the final code of the product to download the program to the NOR FLASH, but the download speed is slower and the running speed is slower than that of the SDRAM. Jeff guessed that we should probably be able to write the program in two sections. When the product is released, starting from the NOR FLASH, the first program of the NOR FLASH is run, and the second program with the NOR FLASH is loaded into the SDRAM until it is powered off. This will increase the speed. The first three previous modes all use the low optimization level (-O0) optimization, while the _flexspi_nor_release version uses the high optimization (-O3) level in order to save program space and improve operating efficiency. (Jie Jie Tucao: It is a bit long compilation). Tips: If you do not use mdk to see the code, you can remove the "magic stick" -> Output -> Browse Information. Then you can use the source insight to see the code, a lot easier, at least better than the mdk. Enjoy the next code. The routine is to transplant the RT-Thread Internet of Things operating system (or to support the domestic operating system), take a look at the source code. First introduce the RT-Thread Internet of things operating system (hereinafter referred to as rtt), the operating system is lightweight, using very small resources to complete the real-time operating system. These are some of RTT's files, bsp is some board-level related stuff, components are some of the components, see the English words are known. Then src is the source code for the implementation of RTT. Include is some header files, and libcpu is the support of some chips. Tools are some RTT tools. Example will not learn embedded. . . . . Look at the source code is indeed a very lightweight operating system, transplantation is also very simple, the focus is the fire brother has helped us transplant well, directly use it, JJ in the school rtt process, found that with some operating systems or a little Not the same, his startup method is already done in the startup file. come and see: 148 in components.c /* re-define main function */ Int $Sub$$main(void) { Rt_hw_interrupt_disable(); Rtthread_startup(); Return 0; } Turn off interrupts first and start rtt again Int rtthread_startup(void) { Rt_hw_interrupt_disable(); /* board level initalization * NOTE: please initialize heap inside board initialization. */ Rt_hw_board_init(); /* show RT-Thread version */ Rt_show_version(); /* timer system initialization */ Rt_system_timer_init(); /* scheduler system initialization */ Rt_system_scheduler_init(); #ifdef RT_USING_SIGNALS /* signal system initialization */ Rt_system_signal_init(); #endif /* create init_thread */ Rt_application_init(); /* timer thread initialization */ Rt_system_timer_thread_init(); /* idle thread initialization */ Rt_thread_idle_init(); /* start scheduler */ Rt_system_scheduler_start(); /* never reach here */ Return 0; } There are some functions that we implement ourselves, such as the development board initialization: rt_hw_board_init, Rtt is still a bit of fun, the main open to the outside world! We usually write programs are in main.c, so it also engaged in a main_thread_entry thread (in fact, I prefer to call these tasks, but are the same, since the study Rtt, then call the official.) Void main_thread_entry(void *parameter) { Extern int main(void); Extern int $Super$$main(void); /* RT-Thread components initialization */ Rt_components_init(); /* invoke system main function */ #if defined (__CC_ARM) $Super$$main(); /* for ARMCC. */ #elif defined(__ICCARM__) || defined(__GNUC__) Main(); #endif } This function jumps to main in our main.c. The following is where we really implement our code. As mentioned earlier, when RTT is started, the development board related resources are initialized. Therefore, our own main does not need to be initialized, and the opening and starting of the thread of RTT is directly enabled. Lcd_thread = rt_thread_create("lcd", Lcd_thread_entry, RT_NULL, LCD_THREAD_STACK_SIZE, LCD_THREAD_PRIORITY, LCD_THREAD_TIMESLICE); If (lcd_thread != RT_NULL) //Created successfully Rt_thread_startup(lcd_thread); //Start thread Else Return -1; Related macro definitions: #define LCD_THREAD_PRIORITY 13 /* priority, the greater the value, the lower the priority */ #define LCD_THREAD_STACK_SIZE 1024 /* thread stack size in bytes */ #define LCD_THREAD_TIMESLICE 5 /* thread time slice in tick */ Then the implementation of the lcd_thread_entry thread, this definition is fine. Since it is an evaluation, of course, there must be a performance evaluation, a period of use (-O0) low optimization of the integer number of calculations, in the wildfire i.MX RT1052 onboard SDRAM only ran for 21.487 seconds. In the STM32H743 above the 21.479 seconds (400M operating frequency, open CaChe (cache)), and on the stm32f103zet6 ran more than 9 minutes and 57 seconds. Performance can be seen here? If you do not believe you can test on your own, I can wait a few minutes to brush your teeth, and I haven't finished yet. . . . . The test code is as follows: (Test code of source network) Void Calculate() { Unsigned long x; Unsigned long a; a=1; For(x=0;x<4294967294;x++) { a=a+1; } } i.MX RT1052 STM32H743 Stm32f103zet6 In terms of performance, i.MX RT1052 is estimated to be a general MCU that cannot be crossed. Performance is really powerful. The users who read the article may have questions. Obviously, the H7 of the 400M clock speed is faster than the 1052. In this case, Jeff responds. The 1052 is the program on the external SDRAM, and the H7 is on the chip memory, and the H7 has opened the cache. Can it be unpleasant? If this small program runs on the on-chip memory of 1052, it will definitely fly. . . . . However, with such a strong chip, you will not only be able to do this little program. When you run the GUI, you will find the speed. According to the fire brother test, the i.MX RT1052's screen scraping speed is also very fast, the screen with 1366*768 resolution can reach 52HZ, and the 1280*800 screen can reach 60HZ, VCLK clock of about 70MHZ, and occupy 50% of SDRAM. About the data throughput. All In One Intel I5,I5 All In One Pc,All In One Desktop I5,I5 All In One Guangdong Elieken Electronic Technology Co.,Ltd. , https://www.elieken.com