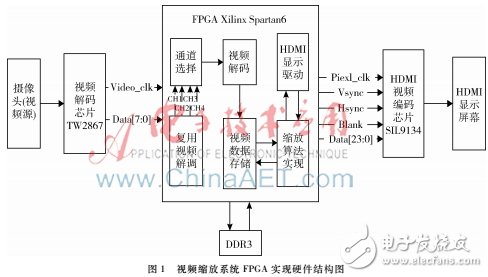

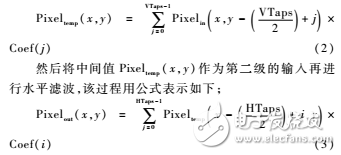

Abstract : Traditional interpolation algorithms have poor processing performance on details when scaling video images, especially when outputting high-resolution video images. Using multi-phase interpolation algorithm to achieve video image scaling, mainly expounds the principle of the algorithm and the hardware structure of the algorithm. The hardware circuit control part uses Xilinx's Spartan6 series FPGA chips. The system can realize the amplification of the video signals collected by the four cameras from any channel to a resolution of 1 920x1 080 @ 60 Hz. The results show that the output video images are real-time and The details remain good. Video image scaling can also be called video image resolution conversion, video image resampling, video image scale conversion, etc. It is one of the key technologies in digital video image processing technology, which directly affects the quality and visual effect of video image output quality Experience. The current video image scaling technology is widely used in medical images, engineering, multimedia, video conferencing and other fields [1]. Traditional video image scaling interpolation algorithms include nearest neighbor interpolation, bilinear interpolation, and bicubic interpolation. Other interpolation algorithms include edge interpolation, B-spline interpolation, and adaptive interpolation. Among them, linear model-based algorithms are used in During image processing, high-frequency signals will be superimposed on the low-frequency signal area, resulting in aliasing of the output video image, especially when the video image output resolution is high, the details will bring a poor visual experience. Multi-phase interpolation algorithm is also a commonly used video image scaling method. Compared with the traditional interpolation algorithm, it has better performance in maintaining details, and is also widely used in industry. The basic principle of video image scaling is to convert the original image with a resolution of (M, N) into a target image with a resolution of (X, Y). Mathematical definition can be described as: known (M, N) pixels, Pixelin (i, j) (i = 1, 2, ..., M; j = 1, 2, ..., N), where i, j Is the pixel coordinate of the original image, and Pixelin (i, j) is the pixel value of the original image. Now we hope to find the output pixels by using a known pixel mapping, Pixelout (x, y) (x = 1,2,…, X; y = 1,2,…, Y), where x, y are the pixel coordinates of the target image, and Pixelout (x, y) is the pixel value of the target image. Then the corresponding function relationship between the pixel values ​​of the input and output images can be expressed as: Pixelout (x, y) = f (i, j, Pixelin (i, j)), the essence of multi-phase interpolation is to solve the target image according to the mapping relationship of the function Pixel values. According to the above analysis, the pixel value of the target image can not be directly obtained from the original image, but needs to be calculated by the position coordinates, pixel value and other information related to the original image. Due to the local correlation of the image content, the pixel value of the output target image is closely related to the pixel value of the input original image adjacent to the corresponding spatial position, and to the pixel value farther from the spatial position. The general video image scaling process is a typical two-dimensional filtering process, which can be expressed by the formula [4] as follows: Pixelout (x, y) = ∑HTapsï¼1i = 0∑VTapsï¼1j = 0Pixelinxï¼HTaps2 + i, yï¼VTaps2 + j & TImes; Coef (i, j) (1) In the formula, HTaps and VTaps are the number of taps of two two-dimensional filters in the horizontal and vertical directions, and Coef (i, j) is the coefficient of the corresponding filter. This coefficient represents the input pixel value to the output pixel value involved in the operation. Weight size. Its value determines the effect of the input pixel value at the corresponding position on the output pixel value and directly determines the scaling effect. The determination of the coefficient depends on the requirements of the filter low pass and anti-aliasing. Figure 1 FPGA implementation hardware structure diagram of video scaling system The two-dimensional structure is more complicated in data operation. In order to simplify the operation, the two-dimensional filter is generally split, and two one-dimensional filters are cascaded to achieve two-dimensional characteristics, that is, horizontal Filters and vertical filters. First, the first stage performs vertical filtering to output the intermediate value Pixeltemp (x, y). The process is expressed as follows: It can be seen from the above analysis that the number of multipliers required before and after the simplified operation is reduced from (VTaps & TImes; HTaps) to (VTaps + HTaps), and the amount of calculation is greatly reduced, which is very beneficial to realize a hardware system with high real-time requirements. At the same time, this idea is also the basic model of hardware implementation of various video image scaling algorithms, that is, the horizontal and vertical directions are separately processed, so that the problem becomes the analysis and processing process of the one-dimensional signal sampling rate change. The system hardware structure is shown in Figure 1. The Xilinx Spartan6 series FPGA chip is used to verify the multi-phase interpolation scaling algorithm. The system uses four analog cameras to collect video signals as the input source. The TW2867 multi-channel video decoding chip converts the analog video signals into digital video signals and sends them to the FPGA chip for data processing. FPGA first performs certain preprocessing on the input data signals. Because the refresh rate of the collected image is inconsistent with the output display image, in order to ensure the matching of the reading and writing rate during data processing, it is necessary to write the image data to DDR3 and then read the data for scaling processing and then output. Finally, through the SIL9134 video encoding chip, the output data signal is encoded into a video stream and transmitted to the screen display to view the output effect. 2.1 Introduction to related chips 2.1.1 Video decoding chip

Put the Airpord Case in the leather case , it will protect your Airpord.We sell airpord case cover,hot selling airpord case,customized airpord cases,etc.

We employ the most creative designers and tech brilliant engineers to make the best cases. We believe our high-quality products with competitive prices will satisfy your needs.

The productive process :

Make the Products Mould –Cutting the fabric –Do the half products – Finish products – Cleaning –QC- Package – Shippment .

airpods case custom,airpord case,airpord case cover,hot selling airpord cases Ysure Leather case 24/7 Support : 86 13430343455 , https://www.ysurecase.com